Advanced Semiconductor Packaging Technologies in Data Centers: The Growth Drivers and the Cutting-Edge Use Cases

Semiconductors are the critical component that enables our digital life. Their development has come a long way; In 1971, the Intel 4004, which was the first single-chip processor, had just 2,250 transistor counts, as of 2022, the most advanced processor has over 50 billion transistor counts! However, advancement comes at a price - both development and production costs have risen to the point that the industry is seeking an alternate solution to manage costs while continuing to deliver advanced products. Alongside this, there is the demand for smaller devices, the necessity for compact integration of heterogeneous components, and the need for higher interconnection densities, which is why advanced semiconductor packaging has entered center stage.

In this article, we will cover the growth drivers of advanced semiconductor packaging technologies on data center applications, as well as give several examples of cutting-edge commercial server products that adopt advanced semiconductor packaging technologies. The content of this article is from IDTechEx's newly released market research report, "Advanced Semiconductor Packaging 2022-2033". The applications of advanced semiconductor packaging technologies covered in the report encompass beyond data centers to autonomous vehicles, 5G&6G, and consumer electronics.

Advanced Semiconductor Packaging Technologies - A Critical Foundation for Next Generation ICs for High Performance Computing Applications/Data Centers

When designing a high energy-efficient system for high performance computing (HPC) applications and data centers, there are three trends related to Si: more transistors, more memories, and more interconnections between the logic IC and the memory. More transistors would require, amongst many challenges, chip design to go beyond the reticle limit, which is beyond the scope of advanced semiconductor packaging. On the other hand, more memories, which can be achieved through high bandwidth on-chip memory as well as increased I/O counts, and more interconnections between the logic IC and memory, both can be realized by advanced semiconductor packaging technologies.

Besides technological improvement, cost management continues to be a key topic in this area as well. Chiplet design has emerged as a way that helps the vendor to find the balance between cost and performance. Chiplet design is a modular approach to building processors. With chiplet design, different dies/chips can be created using the most appropriate process node, lowering the total cost of device by reducing the use of the state-of-the-art process node (expensive!) for unnecessary parts. Another driver for chiplet design is the need for more I/O. Packaging I/O dies such as SerDes, PCIEs, memory I/O, and so on the same module with processing units utilizing 2.5D or equivalent semiconductor packaging technology allows for increased I/O counts in a system. 2.5D advanced semiconductor packaging is the only technology to enable sub-micron routing available today.

State-Of-the Art Use Cases and Future Development Trend

Let's have a look at some of the most current commercial products that have either used or are likely to implement advanced semiconductor packaging technologies in this industry. Take the adoption in server CPU as an example. The majority of current server CPUs being based on monolithic SoC (system on chip), Intel announced in 2021 that its next generation server CPU, Sapphire Rapids, will be based on a four-chip module interlinked via Embedded Multi-die Interconnect Bridge (EMIB). EMIB is Intel's 2.5D advanced semiconductor packaging solution. Meanwhile, AMD is leveraging the power of 3D advanced semiconductor packaging technologies to stack a cache die directly on top of the processor to boost the performance of its latest server CPU Milan-X (products released in Mar.2022).

AMD claim that the 3D packaging enables a >200x interconnect density compared to regular 2D packaging. With both the 1st and 2nd leading server CPU supplier using advanced semiconductor packaging technologies in their newest state-of-the-art product, it is expected that the field's adoption of advanced semiconductor packaging technologies will only expand. In addition to server CPUs, for other components in the data center, such as accelerators, advanced semiconductor packaging technology has also been adopted already. For example, NVIDIA has been using TSMC's 2.5D packaging technology - CoWoS (Chip on Wafer on Substrate) - for its high-end GPU accelerators since 2016.

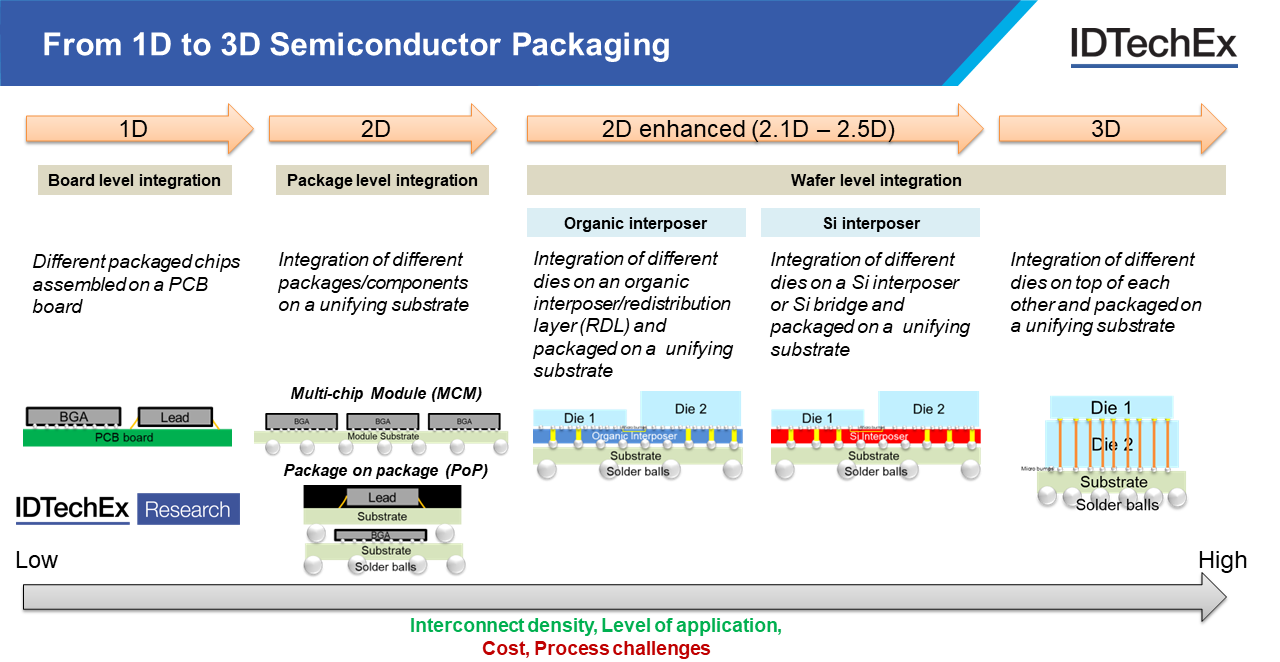

From 1D to 3D Semiconductor Packaging. Source: IDTechEx - "Advanced Semiconductor Packaging 2023-2033"

Even though several high-end commercial products have already used 2.5D advanced semiconductor packaging technologies, numerous development initiatives are currently underway to further improve the performance of such devices and expand the package size to accommodate additional components. The development will progress beyond 2.5D integration. Ultimately, the goal is to have a completely 3D integration where many logic ICs and memory are physically placed on top of one another. However, the road is by no means simple. Thermal management and manufacturing face several problems that have yet to be overcome.

Finally, given the world's expanding need for data centers, advancements in advanced semiconductor packaging technologies, which are crucial to the next generation of integrated circuits (ICs) for high-performance computing applications, will have a substantial market influence.

"Advanced Semiconductor Packaging 2023-2033", a new market research report from IDTechEx, examines the most recent developments and trends in advanced semiconductor packaging technology, key player analyses, and market prospects.

Below lists key aspects of the report:

Technology trends, manufacturer analysis, and market outlook

- Detailed overview of Si IC industry - including technology roadmap and player dynamics

- Analysis of supply chain and business model in the semiconductor IC industry

- Analysis of different semiconductor packaging technologies

- In-depth analysis of key company advanced semiconductor packaging technologies - including the company's state-of-the-art technology and future research development

- Detailed overview of key markets for advanced semiconductor packaging. Including high-performance computing, autonomous vehicles, 5G, and consumer electronics

- Numerous case studies demonstrating the use of advanced semiconductor packaging in variety of applications

- Market scalability of key advanced semiconductor packaging technologies (including 2.5D embedded Si, 2.5 Si interposer, 2.5D (Ultra) high density fanout, and 3D die stacking) in the four primary markets (Data center, Autonomous vehicles, 5G, Consumer electronics) studied by IDTechEx. This information is translated to a 10-year granular market forecasts & analysis

To find out about this IDTechEx report, including downloadable sample pages, please visit www.IDTechEx.com/ASP.

IDTechEx's market research is differentiated through the primary information gathered, technical depth, and unbiased appraisals, IDTechEx covers a wide range of topics and helping understand the industry pain points and unmet needs. For more information visit www.IDTechEx.com/research.